Памяти и накопители Micron 2933 - инструкция пользователя по применению, эксплуатации и установке на русском языке. Мы надеемся, она поможет вам решить возникшие у вас вопросы при эксплуатации техники.

Если остались вопросы, задайте их в комментариях после инструкции.

"Загружаем инструкцию", означает, что нужно подождать пока файл загрузится и можно будет его читать онлайн. Некоторые инструкции очень большие и время их появления зависит от вашей скорости интернета.

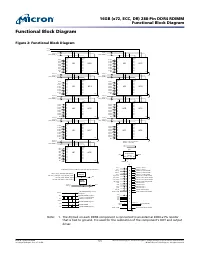

Registering Clock Driver Operation

Registered DDR4 SDRAM modules use a registering clock driver device consisting of a

register and a phase-lock loop (PLL). The device complies with the JEDEC DDR4 RCD

specification.

To reduce the electrical load on the host memory controller's command, address, and

control bus, Micron's RDIMMs utilize a DDR4 registering clock driver (RCD). The RCD

presents a single load to the controller while redriving signals to the DDR4 SDRAM de-

vices, which helps enable higher densities and increase signal integrity. The RCD also

provides a low-jitter, low-skew PLL that redistributes a differential clock pair to multiple

differential pairs of clock outputs.

Control Words

The RCD device(s) used on DDR4 RDIMMs, LRDIMMs, and NVDIMMs contain configu-

ration registers known as control words, which the host uses to configure the RCD

based on criteria determined by the module design. Control words can be set by the

host controller through either the DRAM address and control bus or the I

2

C bus inter-

face. The RCD I

2

C bus interface resides on the same I

2

C bus interface as the module

temperature sensor and EEPROM.

Parity Operations

The RCD includes a parity-checking function that can be enabled or disabled in control

word RC0E. The RCD receives a parity bit at the DPAR input from the memory control-

ler and compares it with the data received on the qualified command and address in-

puts; it indicates on its open-drain ALERT_n pin whether a parity error has occurred. If

parity checking is enabled, the RCD forwards commands to the SDRAM when no parity

error has occurred. If the parity error function is disabled, the RCD forwards sampled

commands to the SDRAM regardless of whether a parity error has occurred. Parity is al-

so checked during control word WRITE operations unless parity checking is disabled.

Rank Addressing

The chip select pins (CS_n) on Micron's modules are used to select a specific rank of

DRAM. The RDIMM is capable of selecting ranks in one of three different operating

modes, dependant on setting DA[1:0] bits in the DIMM configuration control word lo-

cated within the RCD. Direct DualCS mode is utilized for single- or dual-rank modules.

For quad-rank modules, either direct or encoded QuadCS mode is used.

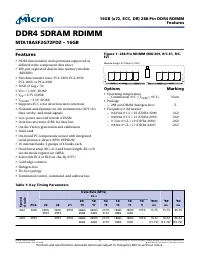

16GB (x72, ECC, DR) 288-Pin DDR4 RDIMM

Registering Clock Driver Operation

CCMTD-1725822587-9899

asf18c2gx72pdz.pdf - Rev. H 7/19 EN

14

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2015 Micron Technology, Inc. All rights reserved.

Характеристики

Остались вопросы?Не нашли свой ответ в руководстве или возникли другие проблемы? Задайте свой вопрос в форме ниже с подробным описанием вашей ситуации, чтобы другие люди и специалисты смогли дать на него ответ. Если вы знаете как решить проблему другого человека, пожалуйста, подскажите ему :)